# microSDカード TLC:64-512GB aTLC:16-128GB

(ET1289+SanDisk Bics5 3D-TLC)

データシート

株式会社アドテック

# **R**EVISION **H**ISTORY

| Revision | Description  | Date      |

|----------|--------------|-----------|

| V1.0     | New release  | July 2023 |

| V1.1     | Added 512GB. | May 2024  |

## **1. Product Introduction**

#### 1.1. Overview

The Industrial microSD Card is designed for demanding industrial applications.

The Industrial microSD Card is compatible with SD 3.0 and provides excellent performance.

The built-in auto ECC function can detect and correct errors during data transfer.

Moreover, the Industrial microSD Card supports Ultra High Speed (UHS) interface transfer mode, provides high write/read data transfer rate, high random IOPS, sudden Power-Fails protection, adaptive static wear-leveling, read/program disturb management, etc.

It was designed to meet the high quality, high reliability, high performance, and versatile environmental requirements.

## 1.2. Product Features

- Interface: 8 pins microSD standard interface

- Compliant SD Card Specification Ver. 3.01 / 4.1 / 5.1 / 6.1

- Density support:

- 3D-TLC:64GB~512GB

- 3D-aTLC (Advanced TLC, single bit per cell TLC): 16GB~128GB

- Bus Speed Mode:

- DS-Default Speed mode: 3.3V signaling, frequency up to 25MHz, up to 12.5MB/sec

- HS-High Speed mode: 3.3V signaling, frequency up to 50MHz, up to 25MB/sec

- SDR12: 1.8V signaling, frequency up to 25MHz, up to 12.5MB/sec

- SDR25: 1.8V signaling, frequency up to 50MHz, up to 25MB/sec

- SDR50: 1.8V signaling, frequency up to 100MHz, up to 50MB/sec

- SDR104: 1.8V signaling, frequency up to 208MHz, up to 104MB/sec

- DDR50: 1.8V signaling, frequency up to 50MHz, sampled on both clock edges, up to 50MB/s

- Operating at -25°C to 85°C

- Flash: 3D-TLC NAND Flash (SanDisk Bics5)

- Controller: ET1289

- Program/Erase Cycle:

- TLC: 3,000 Cycles

- aTLC: 30,000 Cycles

- Built-in ECC corrects up to 120bits/1 KB

- Read disturbance management (Auto-Refresh)

- Adaptive wear leveling

- Management of sudden power-fails

- SMART Function support

- aTLC (Advanced TLC, single bit per cell TLC) support, enhance the performance and product endurance

#### 1.3. TBW (Tera Bytes Written)

| Capacity | 16GB    | 32GB    | 64GB     | 128GB    | 256GB   | 512GB   |

|----------|---------|---------|----------|----------|---------|---------|

| TLC      | -       | -       | 112.6TB  | 225.3TB  | 450.5TB | 900.9TB |

| aTLC     | 366.9TB | 735.3TB | 1470.1TB | 2932.9TB | -       | -       |

\*The endurance of disk could be varying based on user behavior, NAND endurance cycles, and write amplification factor. It is not guaranteed by flash vendor.

\*Client workload by JESD-219A

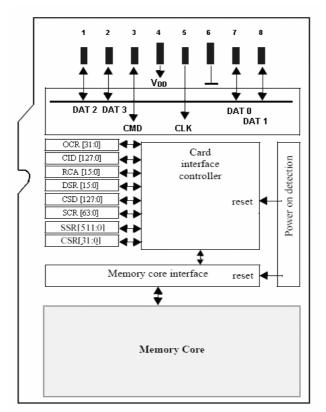

## 2. microSD Card Interface Description

## 2.1 microSD Pin Assignment

| Pin # | Name    | Туре | SD Description                 |

|-------|---------|------|--------------------------------|

| 1     | DAT2    | I/O  | Data Line [Bit2]               |

| 2     | CD/DAT3 | I/O  | Card Detect / Data Line [Bit3] |

| 3     | CMD     | PP   | Command / Response             |

| 4     | VDD     | S    | Supply Voltage                 |

| 5     | CLK     | Ι    | Clock                          |

| 6     | VSS     | S    | Supply Voltage Ground          |

| 7     | DAT0    | I/O  | Data Line [Bit 0]              |

| 8     | DAT1    | I/O  | Data Line [Bit 1]              |

#### Table 1: SD Bus Mode Pin Definition

Notes:

1) S: power supply; I: input; O: output using push-pull drivers; PP: I/O using push-pull drivers.

2) The extended DAT Lines (DAT1-DAT3) are input on power up. They start to operate as DAT lines after SET\_BUS\_WIDTH command. The Host shall keep its own

DAT1-DAT3 lines in input mode, as well, while they are not used. It is defined so, in order to keep compatibility to Multi-media Cards.

3) After power up this line (Pin2) is input with 50Kohm pull-up (can be used for card detection or

SPI mode selection). The pull-up should be disconnected by user,

during regular data transfer, with SET\_CLR\_CARD\_DETECT (ACMD42) command.

| Та | ble 2: SPI Bu | us Mode Pin Definition |  |

|----|---------------|------------------------|--|

|    |               |                        |  |

| Pin # | Name | Туре | SD Description         |  |  |  |

|-------|------|------|------------------------|--|--|--|

| 1     | RSV  |      | Reserved               |  |  |  |

| 2     | CS   |      | Chip Select (neg true) |  |  |  |

| 3     | DI   | I    | Data In                |  |  |  |

| 4     | VDD  | S    | Supply Voltage         |  |  |  |

| 5     | SCLK | I    | Clock                  |  |  |  |

| 6     | VSS  | S    | Supply Voltage Ground  |  |  |  |

| 7     | DO   | 0    | Data Out               |  |  |  |

| 8     | RSV  |      | Reserved               |  |  |  |

Figure 1: Functional Diagram

## 3. Specifications

#### 3.1. Performance

Max. Data Transfer Rate

■ Read: 90MB/s; Write: 70MB/s

#### 3.2. NAND Flash Memory

Industrial microSD Card uses Triple Level Cell (TLC) NAND Flash memory, which is non-volatility, high reliability and highspeed memory storage.

#### 3.3. Power Requirement

#### 3.3.1. DC Input Voltage

■ 2.7V to 3.6V

#### 3.4. Temperature Range

■ -25°C to +85°C

#### 3.5. Humidity

Relative Humidity: 5-95%, non-condensing

#### 3.6. Waterproof

Waterproof level: IEC 60529 IPX8.

| Test Condition                   | Referred standard |  |  |

|----------------------------------|-------------------|--|--|

| Depth of water 1.5m for 30 mins. | IEC 60529 IPX8    |  |  |

#### 3.7. ESD Ability

| Test Condition                                      | Referred standard     |  |  |

|-----------------------------------------------------|-----------------------|--|--|

| <ul> <li>Contact discharge: ± 2KV, ± 4KV</li> </ul> | SD Spec. Appendix D.1 |  |  |

| ● Air discharge: ± 4KV, ± 8KV, ± 15KV               | SD Spec. Appendix D.2 |  |  |

#### 3.8. Dust proof

Dust proof level: IEC 60529 IP6X.

| Test Condition                                    | Referred standard |

|---------------------------------------------------|-------------------|

| Depression of 2 KPa, Talcum powder 2kg/m³, 8 hrs. | IEC 60529 IP6X    |

## 4. Electrical Specifications

#### 4.1 General DC Character

| Parameter                             | Symbol | Min  | Мах | Unit | Remark |

|---------------------------------------|--------|------|-----|------|--------|

| Peak voltage on all lines             | _      | -0.3 | 3.6 | V    |        |

| All input leakage current             | _      | -10  | 10  | μA   |        |

| All output leakage current            | _      | -10  | 10  | μA   |        |

| Supply voltage for low voltage range  | Vddl   | _    | _   | V    |        |

| Supply voltage for high voltage range | Vddh   | 2.7  | 3.6 | V    |        |

| Supply voltage differential           | _      | -0.5 | 0.5 | V    |        |

#### Table 3: General DC Character

#### 4.2 Bus Signal Line Loading

| Parameter                                  | Symbol | Min | Мах | Unit | Remark |

|--------------------------------------------|--------|-----|-----|------|--------|

| Pull up resistance for SD command line     | Rсмр   | 4.7 | 100 | KΏ   |        |

| Pull up resistance for SD data line        | Rdat   | 10  | 100 | KΩ   |        |

| Total Bus capacitance for each signal line | CL     | —   | 30  | pF   |        |

| Signal line inductance                     | _      | _   | 16  | pF   |        |

| Pull-up resistance inside card (pin 1)     | Rdat3  | 10  | 150 | KΩ   |        |

#### **Table 4: Bus Signal Line Loading**

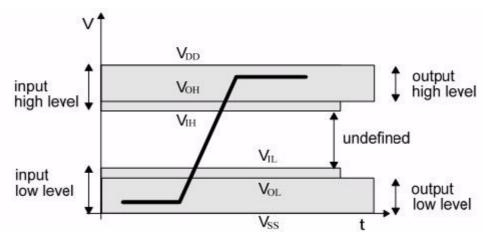

#### 4.3 Bus Signal Levels

As the bus can be supplied with a variable supply voltage, all signal levels are related to the supply voltage.

Figure 4: Bus Signal Levels

| Parameter           | Symbol | Min  | Max  | Unit | Remark                 |

|---------------------|--------|------|------|------|------------------------|

| Output High Voltage | Vон    | 2.4  | —    | V    | V <sub>DD</sub> = 3.3V |

| Output Low Voltage  | Vol    | _    | 0.4  | V    | V <sub>DD</sub> = 3.3V |

| Input High Voltage  | VIH    | 2.0  | 3.6  | V    | V <sub>DD</sub> = 3.3V |

| Input Low Voltage   | VIL    | -0.3 | 0.8  | V    | V <sub>DD</sub> = 3.3V |

| Output High Voltage | Vон    | 1.4  | —    | V    | V <sub>DD</sub> = 1.8V |

| Output Low Voltage  | Vol    | _    | 0.45 | V    | V <sub>DD</sub> = 1.8V |

| Input High Voltage  | VIH    | 1.26 | 2.1  | V    | V <sub>DD</sub> = 1.8V |

| Input Low Voltage   | VIL    | -0.3 | 0.58 | V    | V <sub>DD</sub> = 1.8V |

Table 5: Bus Signal Level

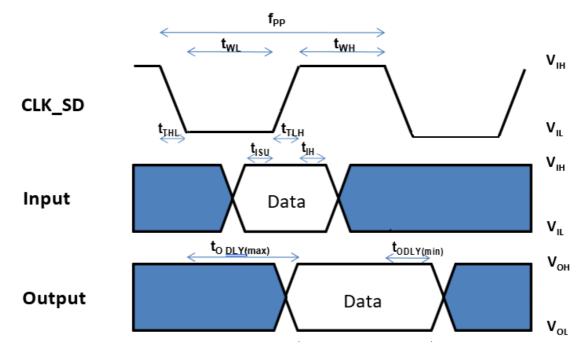

## 4.4 Bus Timing (Default Speed Mode)

#### Figure 5: Timing diagram data input/output referenced to clock (Default Speed Mode)

| Table 6: Bus Timing - Parameters Values (Default Speed) |              |      |      |      |                   |  |  |  |

|---------------------------------------------------------|--------------|------|------|------|-------------------|--|--|--|

| Parameter                                               | Symbol       | Min. | Max. | Unit | Remark            |  |  |  |

| Input CLK_SD                                            |              |      |      |      |                   |  |  |  |

| Clock frequency data transfer mode                      | fpp          | _    | 25   | MHz  | C∟≦ 10pF (1 card) |  |  |  |

| Clock frequency Identification mode                     | fod          | -    | 400  | KHz  | C∟≦ 10pF (1 card) |  |  |  |

| Clock low time / Clock high time                        | tw∟/twн      | 10   | _    | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Clock rise time / Clock fall time                       | tтін/tтні    | _    | 10   | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Input CMD_SD/DATA_SD, referenced to CLK                 | _SD          |      |      |      |                   |  |  |  |

| Input set-up time                                       | <b>t</b> is∪ | 5    |      | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Input hold time                                         | tıн          | 5    | _    | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Output CMD_SD/DATA_SD, referenced to CLK_SD             |              |      |      |      |                   |  |  |  |

| Output Delay time during Data Transfer Mode             | todly        | _    | 14   | ns   | C∟≦ 40pF (1 card) |  |  |  |

| Output Delay time during Identification Mode            | todly        | _    | 50   | ns   | C∟≦ 40pF (1 card) |  |  |  |

aramatore Values (Default Speed)

(1) All timing values are measured relative to 50% of voltage level.

(2) Rise and fall times are measured from 10% - 90% of voltage level.

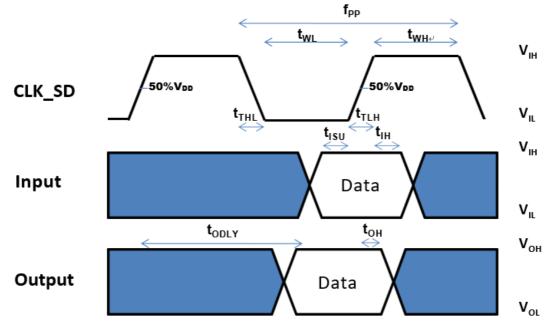

#### 4.5 Bus Timing (High-Speed Mode)

Figure 6: Timing diagram data input/output referenced to clock (High-Speed Mode)

| Table 7: Bus  | Timina .   | . Parameters   | Values | (High-Speed) | ١ |

|---------------|------------|----------------|--------|--------------|---|

| I able 1. Dus | i mining · | - raiaiiieleis | values | (nigh-speed  |   |

| Table 7. Dus Tilling - Parameters Values (mgn-speed) |              |      |      |      |                   |  |  |

|------------------------------------------------------|--------------|------|------|------|-------------------|--|--|

| Parameter                                            | Symbol       | Min. | Max. | Unit | Remark            |  |  |

| Input CLK_SD                                         |              |      |      |      |                   |  |  |

| Clock frequency data transfer mode                   | fpp          | 0    | 50   | MHz  | C∟≦ 10pF (1 card) |  |  |

| Clock low time / Clock high time                     | tw∟/twн      | 7    | —    | ns   | C∟≦ 10pF (1 card) |  |  |

| Clock rise time / Clock fall time                    | tтін/tтні    |      | 3    | ns   | C∟≦ 10pF (1 card) |  |  |

| Input CMD_SD/DATA_SD, referenced to CLK_SD           |              |      |      |      |                   |  |  |

| Input set-up time                                    | <b>t</b> isu | 6    | —    | ns   | C∟≦ 25pF (1 card) |  |  |

| Input hold time                                      | tıн          | 2    | —    | ns   | C∟≦ 25pF (1 card) |  |  |

| Output CMD_SD/DATA_SD, referenced to CLK_SD          |              |      |      |      |                   |  |  |

| Output Delay time during Data Transfer Mode          | todly        |      | 14   | ns   | C∟≦ 40pF (1 card) |  |  |

| Output hold time                                     | tон          | 2.5  |      | ns   | C∟≧ 15pF (1 card) |  |  |

| Total System capacitance for each line               | CL           | _    | 40   | pF   |                   |  |  |

(1) All timing values are measured relative to 50% of voltage level.(2) Rise and fall times are measured from 10% - 90% of voltage level.

| Table 8: Bus Timing - Parameters Values (SDR104/SDR50/SDR25/SDR12) |                  |      |                  |      |                                   |  |

|--------------------------------------------------------------------|------------------|------|------------------|------|-----------------------------------|--|

| Parameter                                                          | Symbol           | Min. | Max.             | Unit | Remark                            |  |

| Input CLK_SD                                                       |                  |      |                  |      |                                   |  |

| Clock frequency data transfer mode                                 | fpp              | 0    | 208              | MHz  | C∟ = 10pF                         |  |

| Clock cycle time                                                   | t <sub>CLK</sub> | 4.8  | —                | ns   | C∟ = 10pF                         |  |

| Clock duty cycle                                                   |                  | 30   | 70               | %    |                                   |  |

| Clock rise time / Clock fall time                                  | ttlh/tthl        | —    | <b>0.2*t</b> ськ | ns   | C∟ = 10pF                         |  |

| Input CMD_SD/DATA_SD, referenced to CLK_SD                         |                  |      |                  |      |                                   |  |

| Input set-up time for SDR104                                       | tisu             | 1.4  | —                | ns   | C∟ = 10pF                         |  |

| Input set-up time for SDR50                                        | <b>t</b> isu     | 3    | —                | ns   | C∟ = 10pF                         |  |

| Input hold time                                                    | tıн              | 0.8  | —                | ns   | C∟ = 5pF                          |  |

| Output CMD_SD/DATA_SD, referenced to CLK_SD                        |                  |      |                  |      |                                   |  |

| Output Delay time for SDR50                                        | todly            |      | 7.5              | ns   | C∟ = 30pF,<br>using driver Type B |  |

| Output Delay time for SDR25 and sdr12                              | todly            |      | 14               | ns   | C∟ = 40pF,<br>using driver Type B |  |

| Output hold time                                                   | tон              | 1.5  | _                | ns   | C∟ = 15pF                         |  |

| Total System capacitance for each line                             | CL               |      | 40               | pF   |                                   |  |

#### Table 8: Bus Timing - Parameters Values (SDR104/SDR50/SDR25/SDR12)

## 4.6 Bus Timing (DDR Mode)

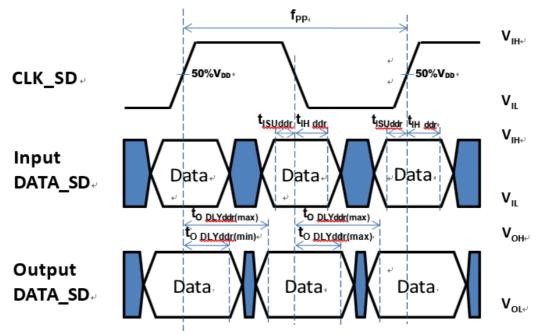

Figure 7: Timing diagram data input/output referenced to clock (DDR Mode)

| Table 9 : Bus Timing - Parameters Values(DDR) |                                    |      |      |      |                   |  |  |  |

|-----------------------------------------------|------------------------------------|------|------|------|-------------------|--|--|--|

| Parameter                                     | Symbol                             | Min. | Max. | Unit | Remark            |  |  |  |

| Input CLK_SD                                  |                                    |      |      |      |                   |  |  |  |

| Clock duty cycle                              |                                    | 45   | 55   | %    |                   |  |  |  |

| Input CMD_SD, referenced to CLK_SD            | Input CMD_SD, referenced to CLK_SD |      |      |      |                   |  |  |  |

| Input set-up time                             | <b>t</b> isu                       | 3    |      | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Input hold time                               | tıн                                | 0.8  |      | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Output CMD_SD, referenced to CLK_SD           |                                    |      |      |      |                   |  |  |  |

| Output Delay time during data transfer mode   | todly                              | _    | 13.7 | ns   | C∟≦ 30pF (1 card) |  |  |  |

| Output hold time                              | tон                                | 1.5  |      | ns   | C∟≧ 15pF (1 card) |  |  |  |

| Input DATA_SD, referenced to CLK_SD           |                                    |      |      |      |                   |  |  |  |

| Input set-up time                             | <b>t</b> ıs∪ddr                    | 3    | _    | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Input hold time                               | tıHddr                             | 0.8  | _    | ns   | C∟≦ 10pF (1 card) |  |  |  |

| Output DATA_SD, referenced to CLK_SD          |                                    |      |      |      |                   |  |  |  |

| Output Delay time during data transfer mode   | $\mathbf{t}_{ODLYddr}$             |      | 7    | ns   | C∟≦ 25pF (1 card) |  |  |  |

| Output hold time                              | <b>t</b> OHddr                     | 1.5  |      | ns   | C∟≧ 15pF (1 card) |  |  |  |

| Table 9 : Bus Timing - Parameters Values(DDR | Table 9 : Bus Timing - | Parameters Values(DDR) |

|----------------------------------------------|------------------------|------------------------|

|----------------------------------------------|------------------------|------------------------|

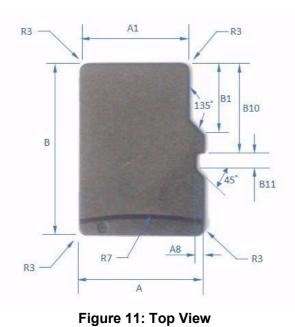

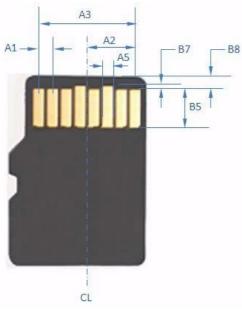

## 5. Mechanical Dimensions

The mechanical dimensions of industrial microSD card were basically followed the mechanical form factor definitions on microSD card specifications which constructed by SD card association.

Figure 12: Side View

Figure 13: Bottom View

| Criteria of | microSI | )     |       | Unit: mm |

|-------------|---------|-------|-------|----------|

| Dimensions  | Min     | TYP   | Max   | Note     |

| А           | 10.90   | 11.00 | 11.10 |          |

| A1          | 9.60    | 9.70  | 9.80  |          |

| A2          |         | 3.85  |       | BASIC    |

| A3          | 7.60    | 7.70  | 7.80  |          |

| A4          |         | 1.10  |       | BASIC    |

| A5          | 0.75    | 0.80  | 0.85  |          |

| A8          | 0.60    | 0.70  | 0.80  |          |

| В           | 14.90   | 15.00 | 15.10 |          |

| B1          | 6.13    | 6.23  | 6.33  |          |

| <b>B</b> 4  | 0.42    | 0.52  | 0.62  |          |

| <b>B</b> 5  | 2.80    | 2.90  | 3.00  |          |

| <b>B</b> 7  | 0.20    | 0.30  | 0.40  |          |

| B8          | 1.00    | 1.10  | 1.20  |          |

| B10         | 7.80    | 7.90  | 8.00  |          |

| B11         | 1.10    | 1.20  | 1.30  |          |

| R3          | 0.70    | 0.80  | 0.90  |          |

| <b>R</b> 7  | 29.50   | 30.00 | 30.50 |          |

| С           | 0.90    | 1.00  | 1.10  |          |

| C1          | 0.60    | 0.70  | 0.80  |          |

| C2          | 0.20    | 0.30  | 0.40  |          |

# 6. Ordering Information

| Flash Type | Part Number       | Capacity | Note |

|------------|-------------------|----------|------|

|            | ADM1U1064G3DEEDES | 64GB     |      |

| TLC        | ADM1U1128G3DEEDES | 128GB    |      |

| TLC        | ADM1U1256G3DEEDES | 256GB    |      |

|            | ADM1U1512G3DEEDES | 512GB    |      |

|            | ADM1U1016GPDEEDES | 16GB     |      |

| aTLC       | ADM1U1032GPDEEDES | 32GB     |      |

|            | ADM1U1064GPDEEDES | 64GB     |      |

|            | ADM1U1128GPDEEDES | 128GB    |      |